FT232HのSYNC 245 FIFOモード(クロック制御編)

FT232HのSync245Modeで、FT232H自体はちゃんと動いているはずなのに、データをロスするという状況を解析してみました。

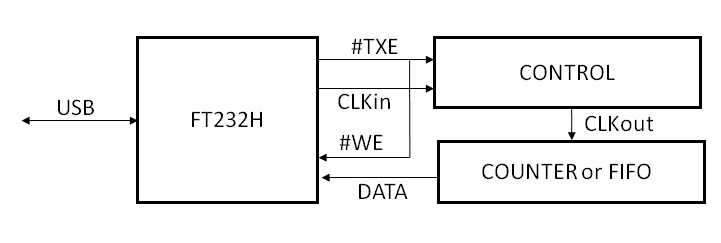

下図のように、Sync Clockによりカウンタもしくは外付けのFIFOメモリなどからデータをPCに転送するとします。

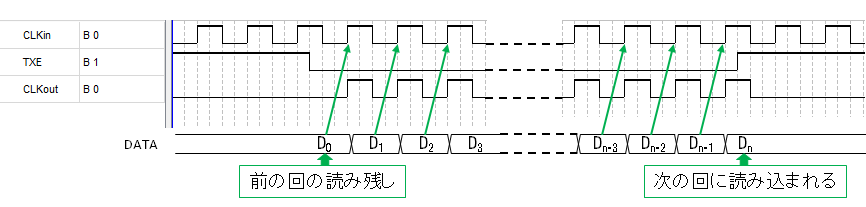

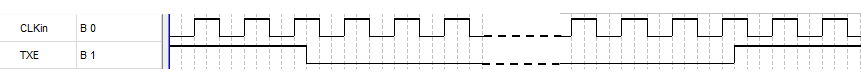

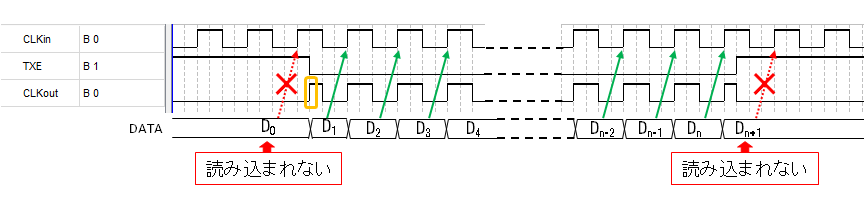

#TXEがLowのときにデータが取り込まれ、Highのときには取り込まれないのですが、FT232Hからのクロックは常に出ています。

なので、#TXEがHighのときにはカウンタotFIFOが動かないようにCONTROLブロックでCLKを止めるようにします。

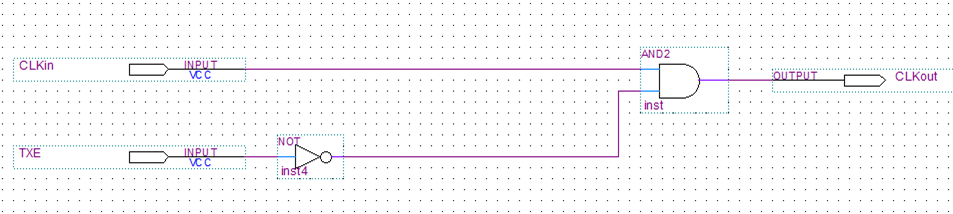

CONTROLブロックを下図のようにすれば、