Data loss issue in FTDI FT232H and FT2232H Sync 245 FIFO Mode (Part1)

FT232H (FT2232H) has SYNC 245 FIFO mode, and this mode works several score times as BitBang mode.

To work FT232H(2232H) in SYNC 245 FIFO mode, it needs to rewrite EEPROM. In this page, I omit how to rewrite.

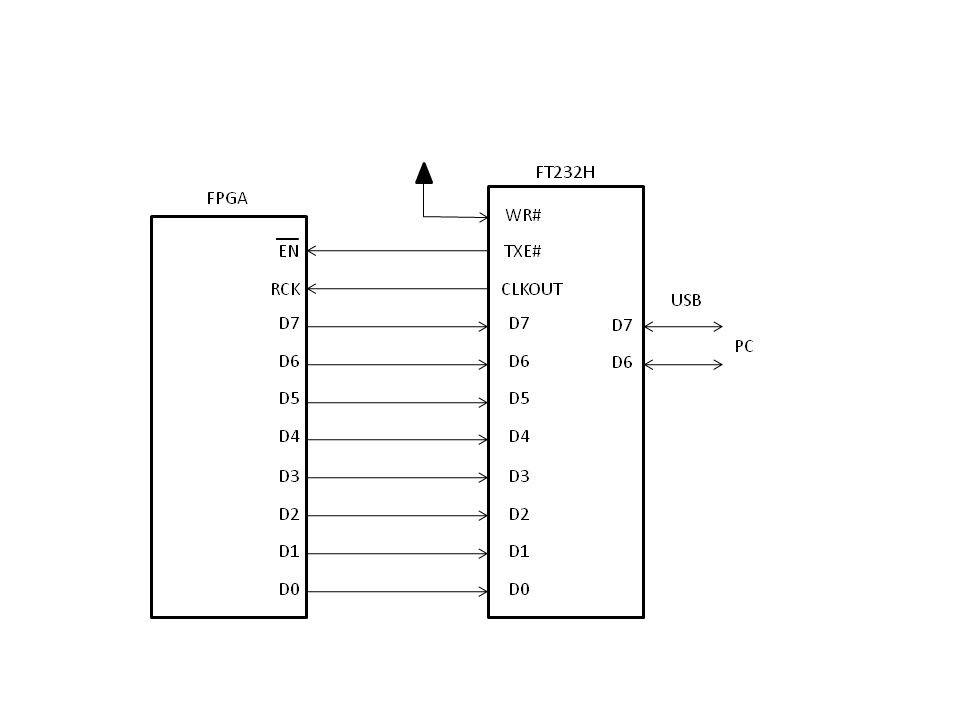

In SYNC 245 FIFO mode, FT232H generates synvronising clock. And connected device (ex.FPGA) can sent data to PC as syncronising with clock.

PC put waiting request signal from the FT232H's TXE# pin (High: data disable).

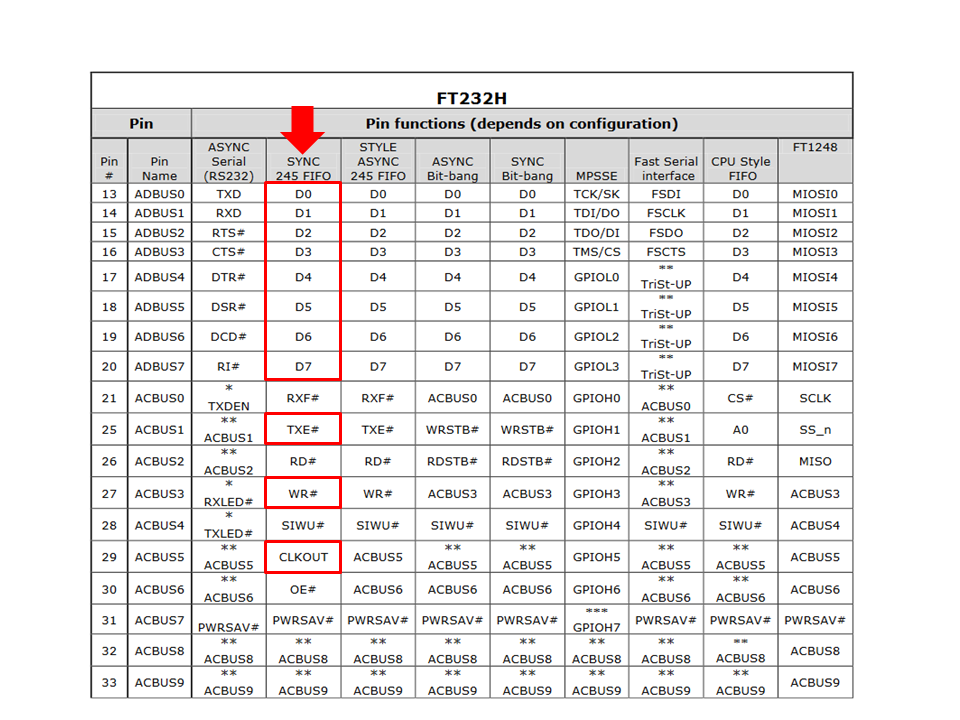

As below table, Data(8bit), clock(1bit), status( 2bit) are enable transfer data to PC.

And FTDI's documents say:

control status only requires TXE#.

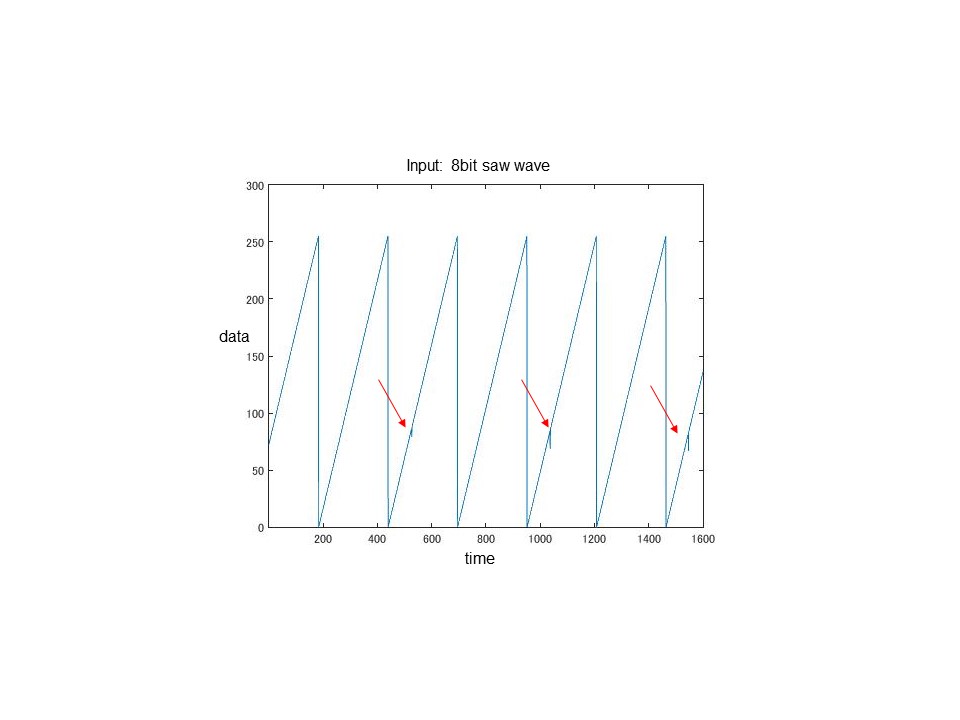

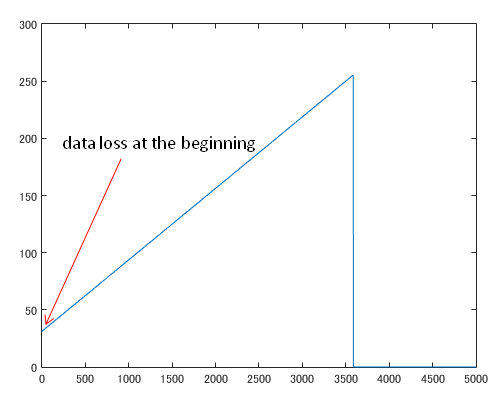

I try Free-run 8bit data output from FPGA to FT232H, but the data loss generated.

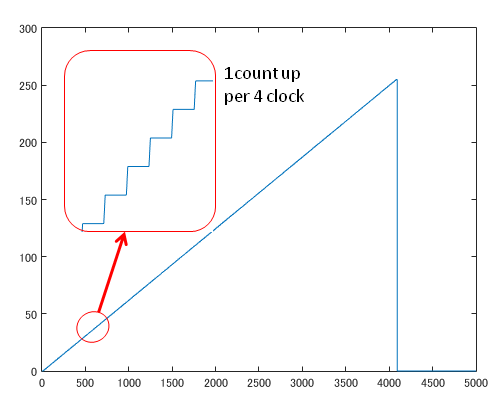

And I tried "once count up data ( 4 times data each step), the begging data was lost.

Continue to Part2